### DESCRIPTION

PT6397 is a Vacuum Fluorescent Display (VFD) Controller. 32 segment/grid output driver lines, one display memory, control circuit and RTC circuit are all incorporated into a single chip to build a highly reliable peripheral device for a single-chip microcomputer and STB application. Serial data is fed to PT6397 via a 4-wire serial interface or I<sup>2</sup>C bus. It is housed in a 52-pin LQFP package.

# **APPLICATIONS**

- Microcomputer peripheral devices

- STB application

## **FEATURES**

- CMOS technology

- Multiple display modes: 32 segments/0 grid to 8 segments/24 grids

- 8-step dimming circuitry

- 3 GPIO ports

- 4-wire serial interface for clock, data input, data output and strobe

- I<sup>2</sup>C bus interface: 400Kbits/s, slave mode only

- RTC circuit:

- Clock counter and calendar counter in BCD format

- Alarm function with interrupt

- 12-hour or 24-hour time display system

- Recognize leap year from the year 2000 to 2099

- Provides RTC display with two segment configuration types: 4-timing & 5-timing formats

- Provides 32 bits segment/grid driver outputs

- No external resistors needed for driver outputs

- Crystal oscillator: 4.194304MHz

- Internal power-on reset

- Available in 52-pin LQFP

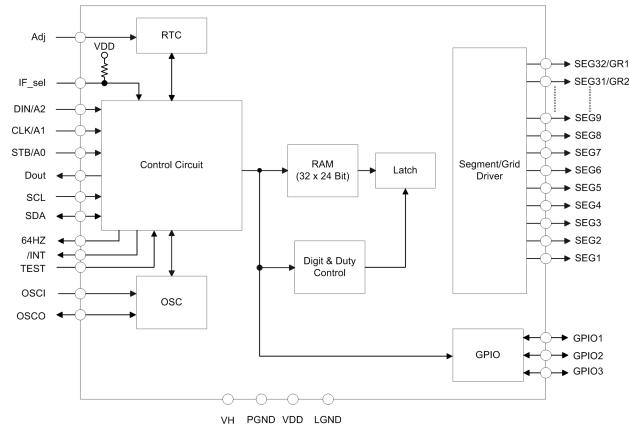

# **BLOCK DIAGRAM**

PT6397

## **1. ORDER INFORMATION**

| Valid Part Number | Package Type  | Top Code  |

|-------------------|---------------|-----------|

| PT6397-LQ         | 52 Pins, LQFP | PT6397-LQ |

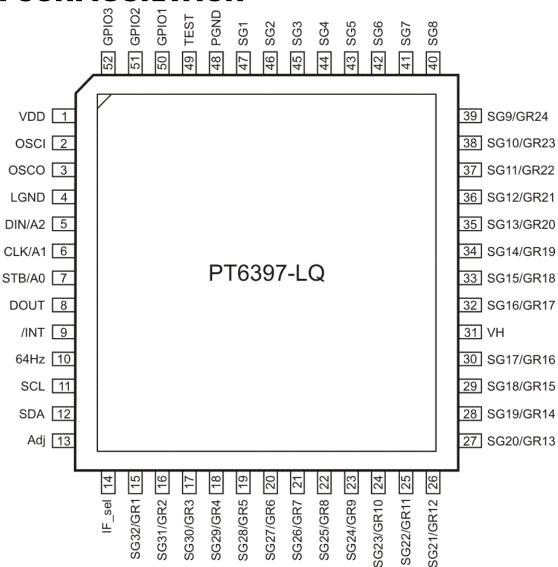

# **2. PIN CONFIGURATION**

## **3. PIN DESCRIPTION**

| Pin Name                    | I/O | Description                                                                                                                                                                                                                                                                                        | Pin No.  |

|-----------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| VDD                         | I   | Logic power supply                                                                                                                                                                                                                                                                                 |          |

| OSCI                        | Ι   | Oscillator input(4.194304MHz crystal input)                                                                                                                                                                                                                                                        |          |

| OSCO                        | 0   | Oscillator output(4.194304MHz crystal output)                                                                                                                                                                                                                                                      |          |

| LGND                        | -   | Logic ground                                                                                                                                                                                                                                                                                       | 4        |

| DIN/A2<br>(Schmitt Trigger) | I   | This pin is data input pin when IF_sel is set to 4-wire serial interface. Data must be ready at the rising edge of CLK (shift-in data must be started from LSB to MSB). The I <sup>2</sup> C device address A2 input pin when the IF_sel is set to I <sup>2</sup> C serial interface.              |          |

| CLK/A1<br>(Schmitt Trigger) | Ι   | Clock input pin when IF_sel is set to 4-wire serial interface.<br>Serial data is read at the rising edge and outputs data is valid at the falling edge.<br>The I <sup>2</sup> C device address A1 input pin when the serial interface is set to I <sup>2</sup> C serial interface.                 |          |

| STB/A0<br>(Schmitt Trigger) | I   | When IF_sel is set to 4-wire serial interface, it is a low-active serial interface strobe pin. The data input after STB actived is processed as a command. When STB is "HIGH", CLK is ignored. The $l^2C$ device address A0 input pin when the serial interface is set to $l^2C$ serial interface. |          |

| DOUT                        | 0   | Data output pin(N-Channel, Open-Drain)<br>This pin is output of serial data at the falling edge of the shift clock(starting from the<br>LSB).                                                                                                                                                      |          |

| /INT                        | 0   | Alarm interrupt pin(N-Channel, Open-Drain)<br>When the setting of alarm date is matched with RTC date, /INT will be set to "0".                                                                                                                                                                    |          |

| 64Hz                        | 0   | OSC's frequency output=4.194304MHz / 2 <sup>16</sup> , Duty=50%                                                                                                                                                                                                                                    | 10       |

| SCL                         | Ι   | The clock pin of I <sup>2</sup> C interface                                                                                                                                                                                                                                                        | 11       |

| SDA                         | I/O | The data pin of I <sup>2</sup> C interface                                                                                                                                                                                                                                                         | 12       |

| Adj (See Note)              | Ι   | Clock adjust. Pulse width must be 3 clocks(OSC) at least.                                                                                                                                                                                                                                          | 13       |

| IF_sel                      | I   | Serial interface mode setting, pull -high with resistor<br>IF_sel: "0" → I <sup>2</sup> C serial interface<br>"1" → 4-wire serial interface                                                                                                                                                        | 14       |

| SG32/GR1 to<br>SG17/GR16    | 0   | High voltage segment/grid output pins                                                                                                                                                                                                                                                              | 15 to 30 |

| VH                          | -   | High voltage driver supply pin                                                                                                                                                                                                                                                                     | 31       |

| SG16/GR17 to<br>SG9/GR24    | 0   | High voltage segment/grid output pins                                                                                                                                                                                                                                                              |          |

| SG8 to SG1                  | 0   | High voltage segment output pins                                                                                                                                                                                                                                                                   | 40 to 47 |

| PGND                        | -   | High voltage driver GND pin                                                                                                                                                                                                                                                                        | 48       |

| Test                        |     | "1": test mode; "0": normal mode                                                                                                                                                                                                                                                                   | 49       |

| GPIO1 to GPIO3              | I/O | General purpose I/O pin, default is set as input port                                                                                                                                                                                                                                              | 50 to 52 |

Note:

The "Adj" pin is used to adjust the RTC, and the adjust is effective by pulse trigger, the following operations are performed by sending a pulse to "Adj" pin.

For minute digits, ranging from "00"  $\sim$  "29" Minute digits of RTC counters which is smaller than 30 are reset to 00. For minute digits, ranging from "30"  $\sim$  "59". Minute digits of RTC counters which is equal to or larger than 30 are reset to 00 and the hour digits are incremented by 1.

Ex.

(X-1) hours, 30 minutes, 0 second

X hours, 0 minute, 0 second  $\rightarrow$ X hours, 0 minute, 0 second

X hours, 29 minutes, 59 seconds

X hours, 30 minutes, 0 second

X hours, 59 minutes, 59 seconds  $\rightarrow$  (X+1) hours, 0 minute, 0 second

(X+1) hours, 29 minutes, 29 seconds

The "year", "month" and "day" will be updated when (X) is the last hours.

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian, Taipei 23145, Taiwan Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw